接口芯片(IC)是否需要配套外部ESD(静电放电)保护器件(通常称为TVS二极管、ESD二极管或ESD保护管),没有一个绝对的是或否的答案,但绝大多数情况下,尤其是在可靠性要求较高的应用中,强烈建议甚至必须使用。

以下是详细的逻辑分析:

- 接口芯片的脆弱性:

接口芯片(如USB、HDMI、Ethernet PHY、RS-232/485、CAN、LVDS收发器等)是系统与外部世界进行物理连接的“门户”。

这些暴露的连接器引脚极易受到外部静电放电(ESD)、电气快速瞬变(EFT)和浪涌(Surge)等瞬态过电压事件的冲击。

虽然现代IC制造工艺会在芯片的I/O引脚内部集成基本的ESD保护结构(通常是二极管到电源和地),但这些内部保护结构的能力是有限的。

- 内部ESD保护结构的局限性:

能量承受能力有限: 内部ESD结构通常设计用于承受人体模型(HBM,典型值如±2kV)或机器模型(MM)等级的ESD事件。它们无法有效吸收和泄放更严酷的ESD事件(如IEC 61000-4-2接触放电±8kV)或能量更大的EFT/Surge的能量。

钳位电压不够低: 当内部保护二极管导通时,它会产生一个钳位电压(Vclamp)。这个电压可能仍然显著高于接口芯片内部核心逻辑电路的耐受电压。即使ESD事件没有立即击穿保护二极管,过高的残留电压也可能损坏后面脆弱的栅氧化层或晶体管。

可能影响信号完整性: 为了提供保护,内部二极管会引入寄生电容。对于高速接口(如USB 3.x, HDMI 2.x, PCIe),这个额外的电容可能会显著劣化信号质量(如增加上升/下降时间,引起反射)。

可靠性风险: 反复经受即使低于其绝对最大额定值的ESD应力,也可能导致内部保护结构逐渐退化,最终失效,降低芯片的长期可靠性。

无法保护电源轨: 内部保护通常针对信号引脚。强ESD事件可能通过信号引脚耦合到电源轨上,导致整个芯片甚至系统复位或损坏。外部ESD保护器件通常能更好地钳位电源轨上的过压。

- 外部ESD保护器件的优势:

更强的能量吸收能力: 专为ESD/浪涌保护设计的TVS二极管具有更大的结面积和散热能力,能够安全泄放IEC 61000-4-2(如±8kV, ±15kV)甚至更高等级的能量。

更低的钳位电压: 优质的外部TVS二极管具有非常低的动态电阻,能在极短时间内(纳秒级)将过压钳位到一个远低于内部保护结构的、对后续电路安全的水平(Vclamp)。

更低的寄生电容: 针对高速接口设计的TVS二极管(如低电容TVS阵列)具有极低的寄生电容(可低至0.3pF或以下),对高速信号的影响微乎其微。

保护电源轨: 可以使用专门的TVS二极管或瞬态抑制二极管来保护电源输入引脚。

提高系统可靠性: 作为“第一道防线”,外部ESD器件吸收了绝大部分冲击能量,大大降低了接口芯片和整个系统因瞬态事件而损坏或失效的风险。

满足合规性要求: 大多数电子产品的行业标准和法规(如IEC/EN 61000-4-2, IEC/EN 61000-4-4, ISO 10605等)明确要求设备需要通过特定的ESD/EFT/Surge抗扰度测试。使用外部ESD保护器件是达到这些严苛测试要求的关键手段。

- 何时可能(谨慎地)考虑不额外使用?

极低成本、一次性、低可靠性要求的应用: 例如,某些玩具或简单消费电子,成本极度敏感,且损坏后果可接受。

完全封闭、无用户可接触接口的系统: 如果接口(如板间连接器)完全封装在机箱内,且机箱设计良好(屏蔽、接地),ESD风险极低。

芯片内部已集成了非常强健的专用保护: 少数特殊设计的接口芯片可能宣称集成了满足IEC标准的强大保护。但这需要仔细审查其数据手册的详细规格和测试报告,并评估其在实际应用中的裕量是否足够。这种情况相对少见,且风险自担。

极其低速、高阻抗的接口: 对信号完整性要求极低,且本身阻抗很高不易引入大电流的情况,风险相对小。但仍不推荐。

- 选择和使用外部ESD器件的关键点:

工作电压: 选择VRWM(反向关断电压)略高于接口正常工作电压的器件。

钳位电压: 选择Vclamp尽可能低的器件,确保低于被保护接口芯片引脚的绝对最大额定电压,并留有足够裕量。

峰值脉冲电流/功率: 根据要满足的ESD/浪涌等级(如IEC 61000-4-2 Level 4)选择具有足够IPP或PPPM能力的器件。

寄生电容: 对于高速接口(>100Mbps),选择超低电容的TVS二极管或阵列。

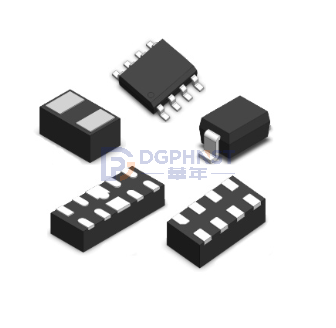

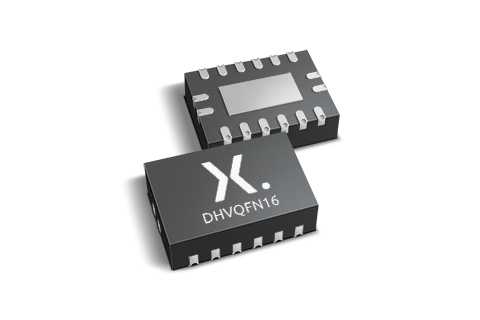

封装和布局: 选择合适封装的器件(如SOD-323, SOT-23, DFN, WLCSP等)。最关键的是,ESD保护器件必须尽可能靠近连接器入口放置,其接地路径必须非常短且低阻抗(直接连接到连接器的金属外壳或系统参考地平面),确保瞬态电流被最短路径旁路到地,而不是流经敏感的电路板走线。

结论:

对于绝大多数包含暴露接口(尤其是用户可接触接口)的电子设备,为其接口芯片配套专用的外部ESD保护器件不是“需不需要”的问题,而是“必须”的工程设计最佳实践。

外部ESD器件弥补了芯片内部保护结构的不足,提供了更强健、更低钳位电压的保护,显著提高了系统抵抗外部静电和瞬态干扰的能力,确保产品的可靠性和符合相关法规要求。在高速接口中,选择低电容的ESD保护器件至关重要。省略外部ESD保护是一种高风险的设计决策,通常只在成本极度敏感且对可靠性要求极低的特殊场景下才可谨慎考虑,并需充分意识到其潜在风险。稳妥且推荐的做法始终是:为接口芯片配置合适的ESD保护管。