电源管理IC(PMIC)的封装技术直接影响芯片的散热性能、电气特性、尺寸适配性及最终应用场景。根据当前行业实践,封装形式可归纳为以下三类,结合典型案例说明其设计逻辑与应用适配性:

一、传统封装形式:成熟工艺,通用性强

- DIP(双列直插式封装)

结构:双排引脚直插PCB通孔,早期标准封装形式。

特点:机械强度高、手工焊接方便,但体积大、引脚密度低(一般≤100脚),散热较差。

典型应用:低功耗电源管理模块(如CL4056E锂电池充电IC的早期版本)或工业控制板中基础稳压电路。

- SOP/SOIC(小外形封装/贴片封装)

结构:表面贴装(SMT),引脚呈“海鸥翼”状从两侧引出。

升级方向:衍生出薄型版本(如TSOP、SSOP),厚度与引脚间距进一步压缩。

代表型号:芯联CL4056E(ESOP8封装),用于1A锂电池充电管理,兼顾小型化与成本控制。

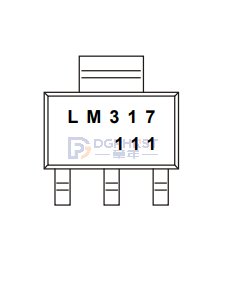

- SOT(小外形晶体管封装)

结构:金属或塑料封装,引脚数少(通常≤6),专为低功率设计优化。

适用场景:穿戴设备中的LDO(低压差稳压器),如耳机充电仓电源管理。

二、先进高密度封装:小型化与高效能的核心

- QFN(无引线四方扁平封装)

革新点:底部设金属散热焊盘,通过PCB导热;无引脚设计减少寄生电感。

优势:高功率密度(如效率96%的同步降压电路)、尺寸紧凑(典型4×4mm)。

案例:南芯NX9813(QFN4x536),支持5V/3.4A快充与TypeC协议,用于移动电源SOC。

- WLCSP(晶圆级芯片尺寸封装)

技术本质:直接在晶圆上完成封装,尺寸≈裸片(无封装基板)。

极限小型化:如Nordic nPM1100(2.075×2.075mm),集成USB充电器+DC/DC降压,用于nRF53蓝牙SoC供电,PCB占板仅23mm²。

- BGA(球栅阵列封装)

设计特点:底部焊球阵列代替引脚,高I/O密度(数百至千级),优异高频特性。

适用领域:多路电源管理PMIC,如服务器CPU供电模块。

三、面向高性能与高集成需求的封装

- LGA(栅格阵列封装)

结构:底部金属焊盘接触PCB,抗振动性强于BGA。

场景:车规级PMIC(如引擎控制单元),需耐受机械应力与高温。

- 3D堆叠封装(如PowerStack™)

技术融合:垂直堆叠多芯片(如控制器+MOSFET),减少互连损耗。

案例:Microchip MCP16701(8×8mm VQFN封装)集成8路降压转换器+4路LDO,用于AI加速卡供电,较分立方案节省48%面积。

封装选择关键维度对比表

| 封装类型 | 引脚形式 | 典型尺寸范围 | 散热性能 | 典型应用场景 |

| DIP | 双排直插引脚 | 较大(>10×10mm) | 低 | 实验板、工业基础模块 |

| SOP/TSOP | 两侧翼形引脚 | 中等(5×6mm) | 中 | 消费电子电源管理IC |

| QFN | 底部焊盘+四周触点 | 紧凑(3×3~5×5mm) | 高 | 快充IC、移动设备PMIC |

| WLCSP | 晶圆级焊球 | 极小(≈芯片) | 中 | 可穿戴设备、微型传感器 |

| BGA/LGA | 全底阵列焊球/焊盘 | 灵活(5×5~40×40mm)| 极高 | 服务器、FPGA配套PMIC |

四、封装选择的核心逻辑

空间限制:穿戴设备首选WLCSP(如nPM1100);移动电源倾向QFN(NX9813)。

功率与散热:>3A电流选QFN/BGA;多路输出需3D堆叠(MCP16701)。

成本与工艺:DIP/SOP适合低复杂度设计;BGA需配套回流焊与X光检测设备。

协议支持:快充/多口输出IC(如USB PD)需高引脚数,推动QFN/BGA普及。

未来PMIC封装将持续向系统级封装(SiP) 演进,融合数字控制、功率器件与无源元件,在AIoT与电动车辆领域实现“功率密度”与“功能集成”的双重突破。